Memory

1. What is Memory IC?

Memory IC is a type of integrated circuit, which is specially used for data storage and read and write operations. It integrates a large number of storage units on a semiconductor chip and controls data access through electronic signals. It has the characteristics of high density, low power consumption, and fast response, and is the core storage component of modern electronic devices.

2. What are the Types of Memory IC?

1) Classification by Volatility

√Volatile Memory:

DRAM (Dynamic Random Access Memory): Needs to be refreshed regularly, commonly used in computer memory (such as DDR).

SRAM (Static Random Access Memory): No need to refresh, fast speed, used for CPU cache.

√Non-Volatile Memory:

ROM (Read Only Memory): Firmware storage (such as BIOS).

Flash: Including NAND Flash (Solid State Drive, USB Flash Drive) and NOR Flash (embedded system boot code).

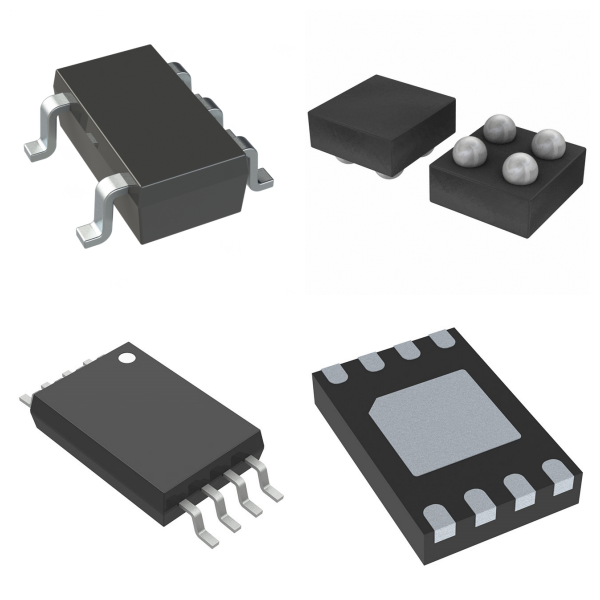

2) Classification by Integration Form

√Independent Storage Chip: such as DRAM chip, NAND Flash chip.

√Integrated Storage Solution:

eMMC: NAND Flash + controller, used for mobile phone/tablet storage.

MCP: Multi-chip package (such as NAND Flash + DRAM), saving space.

3. What are the Key Technical Features of Memory IC?

High Integration: Modern Memory IC can integrate billions of storage units on a single chip (such as VLSI/ULSI level).

Interface Standardization: Supports common interfaces such as SPI, I²C, DDR, etc., which is convenient for system integration.

Power Consumption Control: Adopt low voltage design (such as 1.8V/3.3V) and sleep mode to optimize energy efficiency.

4. Major Manufacturers and Product Forms of Memory IC

Head Manufacturers: Samsung, SK Hynix, Micron (dominate the DRAM/NAND market).

Terminal Products: memory stick (Kingston), embedded storage module (eMMC), memory card (SanDisk), etc.

5. Design Implementation of Memory IC (IC Design Level)

Verilog Modeling: Define storage units through register arrays, for example, reg [7:0] my_memory [0:255] represents a memory with 8 bits wide and 256 bits deep.

Initialization Method: Use system task $readmemh to load initial data from a file to the storage array.

6. Summary

Memory IC is the "data warehouse" of electronic systems, covering multi-level requirements from cache (SRAM) to mass storage (NAND Flash). Its technological evolution continues to promote the performance improvement and miniaturization of electronic devices.